이번에는 ELECTRIC-FIELD 3D(전기장 해석)를 사용하여 반도체 소자 내부의 전기장을 해석해 보겠습니다.

반도체에서의 전기장 해석에 대하여

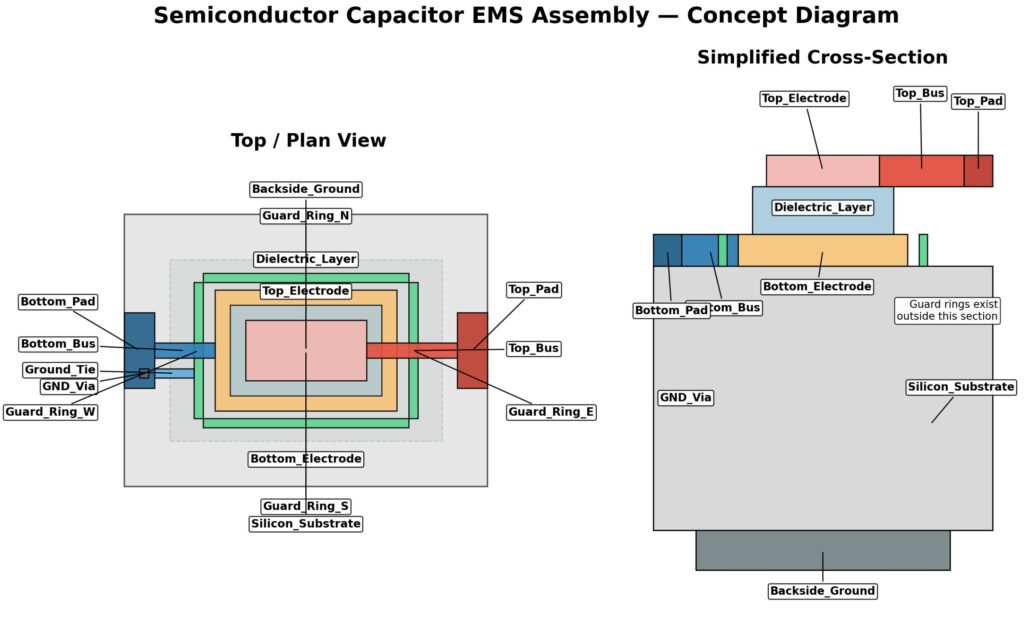

그림 2: 실리콘 캐패시터의 개념도

반도체 내부에서는 전자와 정공이 전기장에 의해 가속되고 이동합니다.

즉, 전기장 분포를 알지 못하면 전류의 흐름, 전하의 축적 방식, 절연 파괴가 일어나기 쉬운 위치, 스위칭 특성 등을 정확히 파악할 수 없습니다.

주요 이유는 아래와 같습니다.

1. 전자와 정공의 움직임을 결정하기 위해

반도체 내의 캐리어는 전기장에 의해 움직이므로, 전기장 분포를 조사하면 전류 경로와 전하 수송 양상을 예측할 수 있습니다. MOSFET, 다이오드, IGBT 등에서는 특히 중요합니다.

2. 고전계에 의한 파괴와 누설을 방지하기 위해

국부적으로 전기장이 너무 강해지면 절연막 파괴, pn 접합의 애벌랜치 파괴, 터널 전류 증가, 누설 증가가 발생할 수 있습니다.

따라서 어디에서 전기장 집중이 일어나는지 해석할 필요가 있습니다.

3. 소자 성능을 최적화하기 위해

전기장 분포는 문턱전압, 온저항, 내전압, 스위칭 속도, 기생 커패시턴스 등에 영향을 줍니다.

해석을 통해 전극 형상, 도핑 분포, 절연막 두께, 가드 링 배치 등을 최적화할 수 있습니다.

4. 미세화될수록 문제가 더 뚜렷해지기 때문에

반도체가 미세해질수록 좁은 영역에 전기장이 집중되기 쉬워집니다.

예전에는 무시할 수 있었던 효과도 미세 소자에서는 단채널 효과나 핫 캐리어 열화처럼 심각해질 수 있습니다.

5. 전력 반도체에서는 내전압 설계와 직접 연결되기 때문에

SiC, IGBT, MOSFET 같은 전력 소자에서는 최대 전기장이 어디에 형성되는지가 내전압을 좌우합니다.

종단 구조나 에지부 설계에서는 전기장 해석이 거의 필수입니다.

6. 시제품 제작 횟수를 줄일 수 있기 때문에

실제로 만들어서 측정하는 방식만으로는 시간과 비용이 많이 듭니다.

전기장 해석을 사용하면 시제품 제작 전에 문제점을 예측하고 설계 방향을 잡을 수 있습니다.

이번에는 반도체의 대표적인 소자인 캐패시터 내부와 그 주변의 전기장에 대해 해석해 보겠습니다.

실리콘 캐패시터의 전기장 해석

ELECTRIC-FIELD 3D를 사용하여 실리콘 캐패시터의 전기장 해석을 수행합니다.

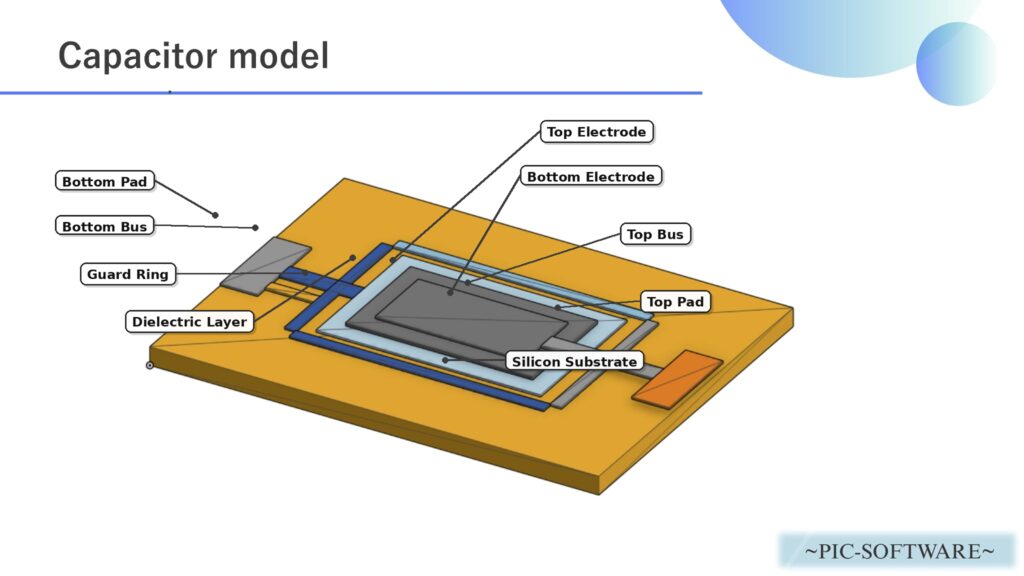

해석 모델은 아래와 같습니다.

해석 모델

그림 2: 실리콘 캐패시터의 해석 모델

위와 같은 실리콘 캐패시터의 해석 모델을 작성하고, 캐패시터 내부와 그 주변의 전기장 분포 해석을 수행했습니다. 각 부품의 역할은 아래와 같습니다.

-

-

-

-

Top Pad

외부에서 상부 전극으로 전기적으로 연결하기 위한 단자입니다. 측정기기나 배선으로부터 신호와 전압이 들어오는 입구가 됩니다. -

Top Bus

Top Pad와 Top Electrode를 연결하는 배선입니다. 상부 전극까지 전위를 전달하는 도체 패턴입니다. -

Top Electrode

캐패시터의 상부 전극입니다. Bottom Electrode와 마주 보며 전기장을 형성하고, 정전용량 형성에 주요하게 관여합니다. -

Bottom Pad

외부에서 하부 전극 측으로 연결하기 위한 단자입니다. GND 측 또는 기준 전위 측의 인출 단자로 사용되는 경우가 많습니다. -

Bottom Bus

Bottom Pad와 Bottom Electrode를 연결하는 배선입니다. 하부 전극에 전위를 전달하는 역할을 합니다. -

Bottom Electrode

캐패시터의 하부 전극입니다. Top Electrode와 한 쌍을 이루며 실제로 전하를 저장하는 상대 전극이 됩니다. -

Dielectric Layer

상부 전극과 하부 전극 사이에 들어가는 절연층입니다. 전류가 직접 흐르지 않도록 하면서 전기장만 통과시켜 캐패시터로 기능하게 합니다.

이 층의 두께와 상대 유전율이 정전용량 값에 크게 영향을 줍니다. -

Guard Ring

주 전극 주변에 배치되는 보조 도체입니다. 가장자리의 프린지 전기장, 누설 전류, 기생 커패시턴스의 영향을 억제하여 측정 안정성과 해석 정확도를 높이기 위해 사용됩니다. -

Silicon Substrate

전체 구조를 지지하는 기판 재료입니다. 기계적 지지체일 뿐 아니라 실제로는 기생 커패시턴스와 전기장 분포에도 영향을 줍니다. 반도체 기판의 경우 전도율과 유전율 설정이 해석 결과에 영향을 미칩니다.

-

-

-

해석 조건

해석 조건은 아래와 같습니다.

| 해석 소프트웨어 | PIC-PLASMA 3D or PIC-ELECTRON 3D or ELECTRIC-FIELD 3D |

| 해석 유형 | 전기장 해석 |

| 해석 오브젝트 | semiconductor.obj |

|---|

- Before

전극, GND, 재료 상수 설정이 불충분한 모델

| 부품 | 전압 | 상대 유전율 εr |

|---|---|---|

| Top_Pad | +5 V | 1.0* |

| Top_Bus | +5 V | 1.0* |

| Top_Electrode | 고정하지 않음 | 1.0* |

| Bottom_Pad | 0 V | 1.0* |

| Bottom_Bus | 0 V | 1.0* |

| Bottom_Electrode | 고정하지 않음 | 1.0* |

| Guard_Ring_W/E/S/N | 고정하지 않음 | 1.0* |

| Ground_Tie | 고정하지 않음 | 1.0* |

| GND_Via | 고정하지 않음 | 1.0* |

| Backside_Ground | 고정하지 않음 | 1.0* |

| Dielectric_Layer | 고정하지 않음 | 1.0 |

| Silicon_Substrate | 0 V 고정 | 1.0 |

- After

| 부품 | 전압 | 상대 유전율 εr |

|---|---|---|

| Top_Pad | +5 V | 1.0* |

| Top_Bus | +5 V | 1.0* |

| Top_Electrode | +5 V | 1.0* |

| Bottom_Pad | 0 V | 1.0* |

| Bottom_Bus | 0 V | 1.0* |

| Bottom_Electrode | 0 V | 1.0* |

| Guard_Ring_W/E/S/N | 0 V | 1.0* |

| Ground_Tie | 0 V | 1.0* |

| GND_Via | 0 V | 1.0* |

| Backside_Ground | 0 V | 1.0* |

| Dielectric_Layer | 고정하지 않음 | 3.9 |

| Silicon_Substrate | 고정하지 않음 | 11.7 |

아래 그림은 이번 해석에 사용한 조건 입력 화면을 ELECTRIC-FIELD 3D에서 나타낸 것입니다.

해석 결과

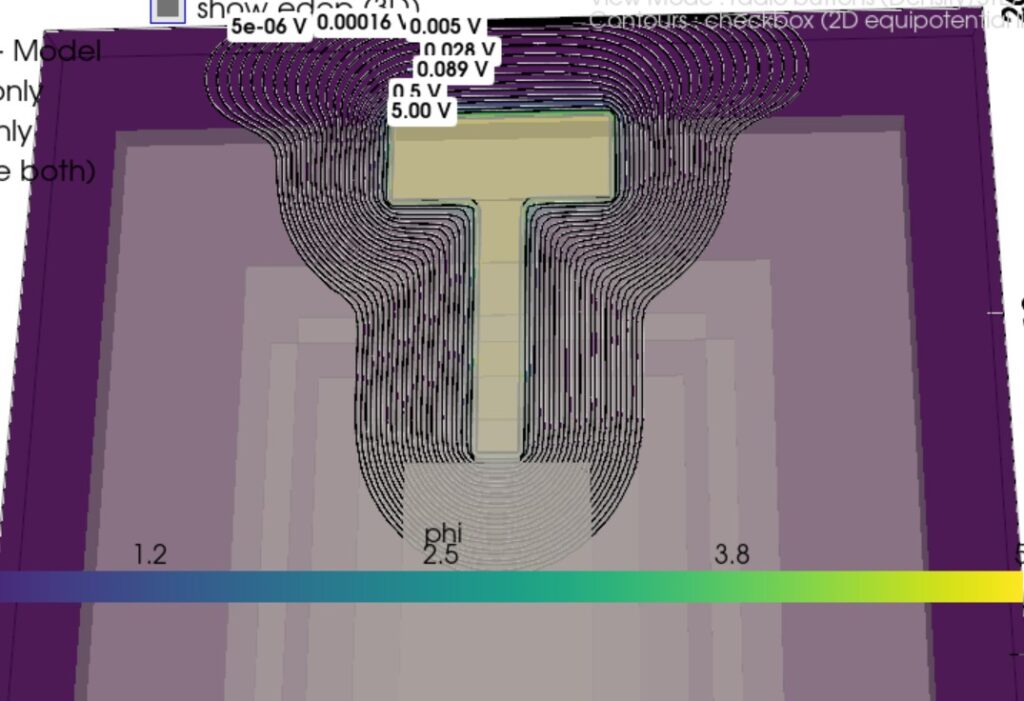

- Before

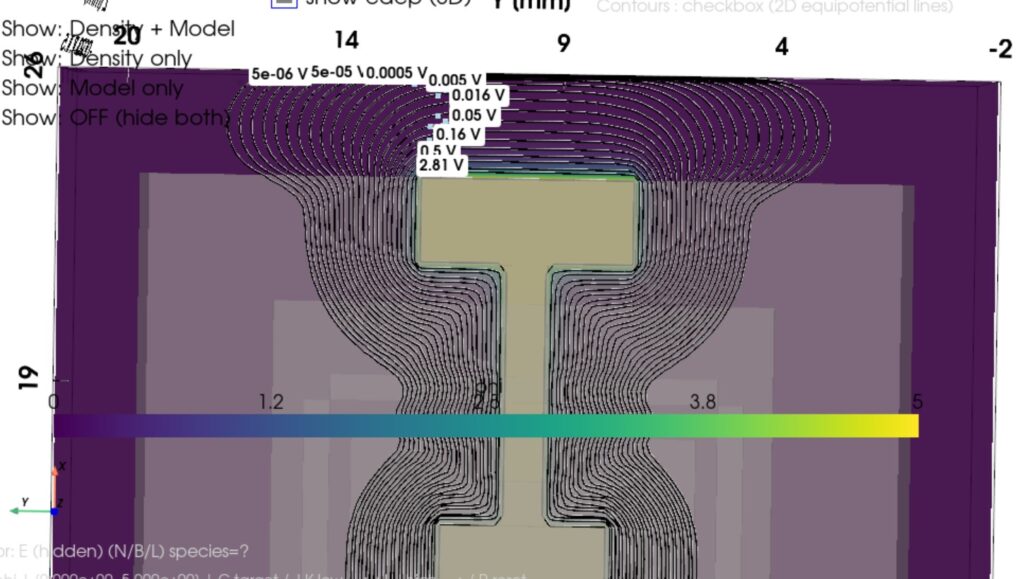

단면

단면

그림 3: 전극, GND, 재료 상수 설정이 불충분한 모델의 전기장 분포

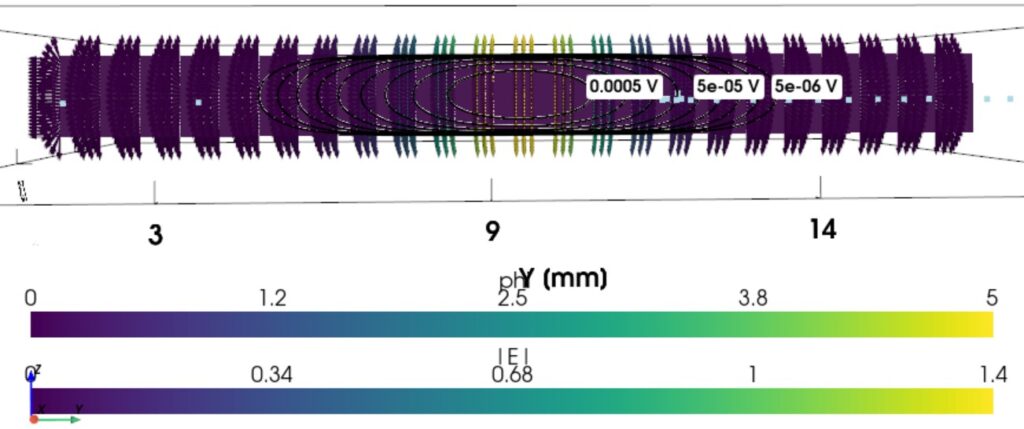

- After

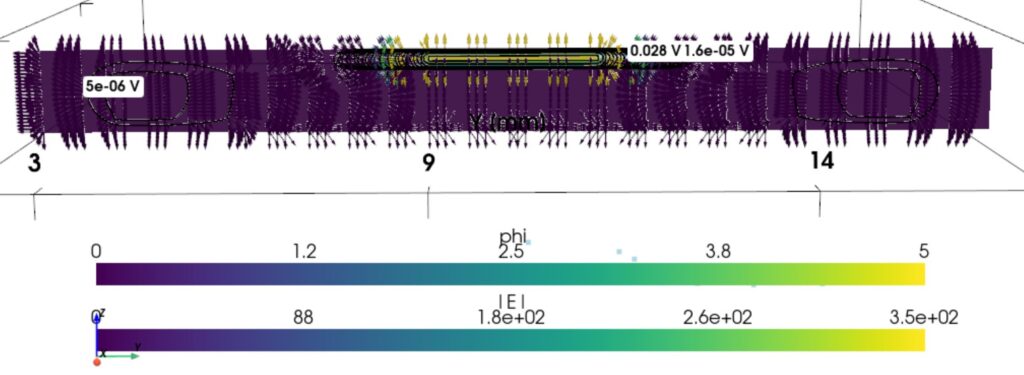

전체

단면

그림 4: 전극 전위, 접지 조건, 재료 상수를 적절히 반영한 모델

그림 4: 전극 전위, 접지 조건, 재료 상수를 적절히 반영한 모델위 자료는 실제로 ELECTRIC-FIELD 3D에서 계산한 실제 해석 결과입니다.

After 조건에서는 주 전극, 상대 전극, 가드 링, 후면 GND의 전위 조건을 적절히 설정함으로써 전기장의 닫힘 구조가 명확해졌고, Before 조건에서 보였던 부유 도체 유래의 불안정한 전기장 분포가 해소되는 결과를 얻을 수 있었습니다.

이번에 사용한 CAD 모델은 간이적으로 제작한 것이므로, 전극 전압과 기타 조건 설정도 간략화되어 있습니다.

※위 내용은 하나의 예시입니다. 제품 개발에 전기장 해석 소프트웨어 ELECTRIC-FIELD 3D를 적극 활용해 보시기 바랍니다.